There are very good reasons for keeping to a synchronous style when constructing an electronic design:

By this stage you should be used to the concept (and advantages) of synchronous design. The most important aspect is that the logic functions can be designed statically; glitches as logic switches don't matter as they can't pass the registers. A clock happens only when everything has settled and everything changes ‘at once’.

A HDL (like Verilog) makes this easy; simply ensure that all state changes use the same clock (and, preferably, the same edge).

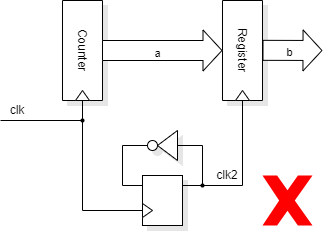

always @ (posedge clk) clk2 <= !clk2;

always @ (posedge clk) a <= a + 1;

always @ (posedge clk2) b <= a;

The timing relationship between the clocks is poorly defined.

Behaviour depends on a race between

a and

clk2.

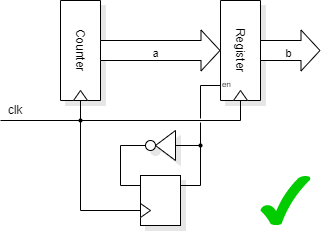

always @ (posedge clk) en <= !en;

always @ (posedge clk) a <= a + 1;

always @ (posedge clk) if (en) b <= a;

Changes happen simultaneously. The ‘en’ signal controls whether a change will happen or not.

Toolchains are geared towards this style of design so they are capable of ensuring that the flip-flops change (near enough to) simultaneously.

It is possible to produce sequential circuits without clocks; indeed much work has been done on this in this Department! There are some potential advantages to asynchronous designs.

However the disadvantages largely outweigh these. (If you didn't follow any of those points, don't worry about them.)

An asynchronous FSM can be constructed from RS flip-flops. (An RS flip-flop is a simple asynchronous FSM!) An input change may then cause one or more flip-flops to change state, which may cause others to change state, and so on until the system restabilises. Care must be taken to ensure no signal can glitch and cause an erroneous state to occur whilst the logic is in transition.

There are some parts of a system where asynchronous signals are unavoidable. External inputs fall into this category. However the usual strategy is to synchronise these to the internal clock as soon as possible.

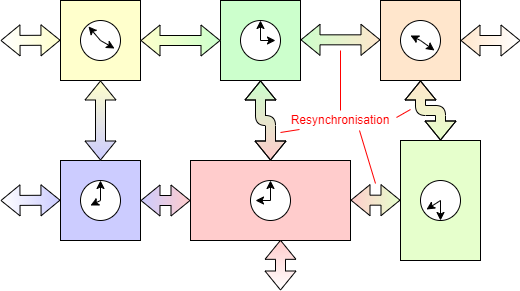

This is a compromise solution which facilitates the production of SoC blocks using conventional CAD tools and processes but bypasses the need for global synchronous clock distribution (which is challenging) and verification (which is also difficult). As the scope of chips gets larger it becomes convenient to restrict synchronous operation to particular assemblies and worry less about the differences in clocks between them. However the each assembly can be synchronous internally and this is usually a good plan. A little more on this topic is covered under ‘interconnection’ where clock-domain crossing is considered.

An advantage of a GALS device is that the clock rate of different blocks can be different. Clocks can be slowed – or stopped – to save power; inactive blocks may even be ‘turned off’ for this reason.

Back to FSMs.

Forwards to look at opportunities for parallelism.

Up to Tradeoffs.