When a state-holding element is switched on it will settle into a stable state.

It is not predictable what state this will be, so it is unknown.

Does this matter? In some cases it does, in others it doesn't.

Example: RISC-V registers

I.e. only the essential values are cleared Rule of thumb:

Undefined (“unknown”) values tend to propagate through logic.

This is usually a good thing as it acts as a warning that something is wrong. Learn to exploit them!

The question of whether to include a reset on a flip-flop has no simple answer.

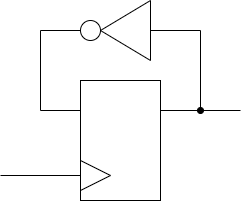

Case: consider a clock divider flip-flop:

As a circuit this will function because it is in some digital state and will toggle to the other when clocked.

In simulation it will start unknown and always remain that way.

In Verilog you could ‘cure’ this anomaly with an ‘initial’; but if that is accidentally done to something where the phase matters then it's doom again.

In general:

Some designers prefer to reset every flip-flop as a matter of routine.

(There is a small additional cost in size and speed.)

You have to decide which approach works for you.

RAM does not have reset. If you expect a RAM to contain some values (typically zeroes) you will have to write these in actively.

Some form of reset signal is vital, at least for a subset of the flip-flops. These are primarily those concerned with control state. Without a reset flip-flops will power-up in an unknown state.

In a physical circuit it may be that (e.g.) an FSM will ‘naturally’ progress into a stable state (like an ‘idle’ state) and await legitimate input — and it makes sense to design it this way. However this will not help in simulation and you do need to verify your designs!

The state of an FPGA is downloaded when it is configured. This means:

This means, for example:

The second of these allows the creation of on-chip ROMs, useful (for example) in bootstrapping a processor or providing look-up tables.

Note that these facilities are provided because of the particular FPGA characteristics. They would not be available on an ASIC.

Unknown/undefined states are a characteristic of digital simulation. Verilog simulation is digital, with signals adopting states {‘0’, ‘1’, ‘x’, ‘z’} and these have well-defined operations. For example:

0 && x == 0

1 && x == x

Digital (functional) simulation does not represent intermediate states, transition (edge) speeds etc.

Not all simulators work this way. Circuit-level simulators represent the analogue voltages on the wires to give more accurate estimates of the behaviour of the implementation. These values are (in principle) continuous, therefore always ‘known’, therefore they have to be assumed at start-up.

Unknown values will not appear. However the assumed values may not be those which occur in a real circuit and therefore should not be relied on.

This is another good reason for running a functional simulation as part of the design flow.

Up to simulation

Back to simulation events

Forward to simulation result treatment