Pages marked ☆ should be revision from COMP12111 or COMP22111.

The synchronous model is not the only means to build computing machinery but it provides an enormous simplification in designing working Finite State Machines. Because of this it is widely supported by CAD tools languages etc. It assumes time is discrete: the next state of a (‘whole’) system can be derived from its current state and its (synchronised) inputs and it changes in response to a ‘global’ stimulus – i.e. a clock.

For this to work there is an assumption that the clock reaches (all)

devices ‘simultaneously’.

i.e. there is minimal clock skew.

The D-type Flip-Flop (DFF) is the current device-of-choice for most state holding within ‘logic’ circuits. (The other major state holding element is RAM – in its various incarnations.) DFFs are used both individually (typically as part of logic control and together to form registers.

An ideal DFF will transfer the state of its data input to its output instantaneously in response to a(n instantaneous) clock edge. Of course, in reality these changes are not instantaneous: every change takes some finite time.

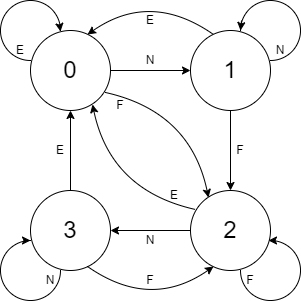

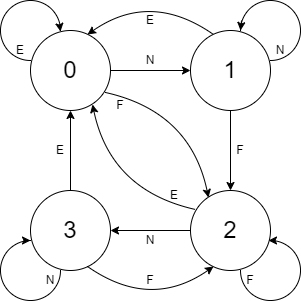

In the synchronous model it is assumed that one flip-flop can feed another which means this (points to figure on right) is possible.

It is important to meet all the flip-flop timing constraints if a circuit is to work under all circumstances. However observe:

If a set up violation is introduced (oops!) it can be avoided by increasing the clock period†. A hold-time violation is fatal however, since nothing can be done externally.

Don't worry too much; most CAD tools will look for possible hold violations and add some buffers (‘do nothing’ logic) to slow down signals which would otherwise be too fast. You might see this in synthesis reports.

†Assuming the application can tolerate the slow-down.

Many variations of DFFs with additional inputs may be present in a parts library. From the HDL perspective this doesn't typically matter but for completeness here are some not-uncommon additional inputs:

†May or may not supersede a synchronous set/clear.